### Electrical Harmonics 101

An Overview of the Fundamentals of Electrical Harmonics and Discussion of Mitigation Strategies.

Michael A. McGraw

11135 lota Dr. San Antonio, TX 78217 210-492-4200 800-229-8965

www.vfd.com

#### General Discussion

- As new technologies for load-based structures continue transitioning to modern diode bridge and IGBT based rectification configurations, electrical harmonics play a key consideration in power quality specifications and design of the distribution grid.

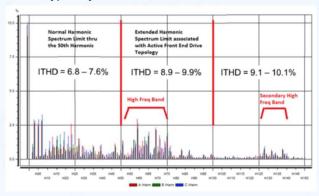

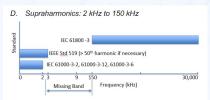

- Many utilities within the US, and around the world, are increasingly requiring customers to comply with the relevant harmonic standards in their region. In the United States and Canada, IEEE Std 519-2022 is the foundation of most provider-based PQ requirements for low frequency harmonic applications (3 kHz or less). For high frequency applications (150 kHz and above) IEC 61800-3 can be applicable and referenced. The result being that there is an entire bandwidth of potential harmonic frequencies where no active standards make recommendations for current or voltage harmonic limits (3 kHz - 150 kHz). The closest thing is that IEEE Std 519 has an allowance to include harmonics above 50th when 'necessary'.

- Little is taught or covered about the applicational challenges of harmonic mitigation and the "best practices" in design and specifications to ensure proper load structure power quality. \*IEEE published paper references and other White Paper Sources will be included for reference and referral.

#### Content

- Develop a fundamental understanding of electrical harmonics from a load and source potential perspective.

- \* Key relationships between current harmonic and voltage distortion due to source impedance.

- \* A review of systemic resonance.

- \* True/Total Power Factor versus Displacement Power Factor and the role of Harmonic Capacitance Reactance.

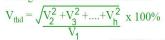

- A review of IEEE Std 519-2022 and understanding current distortion (Ithd and/or Itdd) and voltage distortion (Vthd) requirements.

- A summary review of existing and new installation harmonic mitigation strategies currently being deployed within many industries (Staged and Partial Mitigation Strategies)

3

#### Fundamentals of Electrical Harmonics

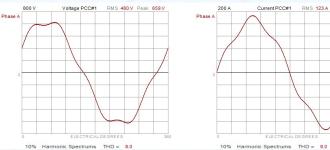

Non-linear loads draw current in a Non-Sinusoidal manner, where the fundamental 60 Hz frequency is impacted by higher frequency current draws from the switching frequency of the rectifier segment of the load device. Typically, we associate this with ASD/VFD applications but it will exist in:

Diode Bridge or IGBT rectifier loads. UPS, DC rectifiers, and inductive heating systems.

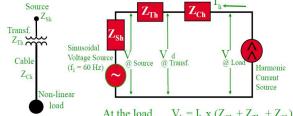

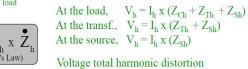

The current draw characteristic then impacts the system voltage regulation, i.e. the instantaneous change in current negative and positive (di/dt) will create a corresponding change in the system voltage rate of change (dv/dt) of the source.

The injection of the current harmonic into the system impedance creates voltage distortion.

The weaker the system the greater the Vthd (Total Harmonic Distortion – Vthd) and the lower the Ithd (Total Harmonic Distortion – Current)

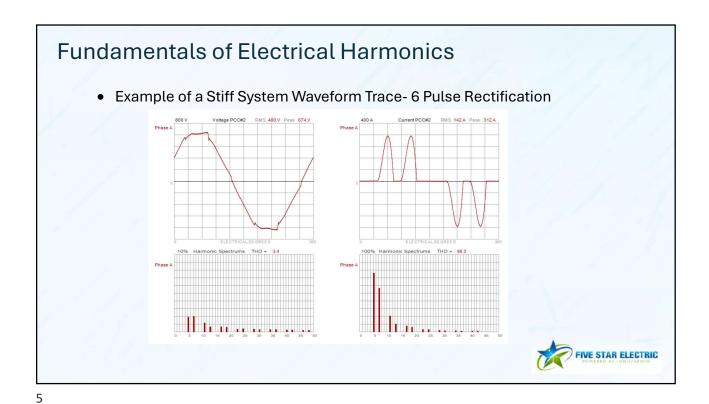

Fundamentals of Electrical Harmonics

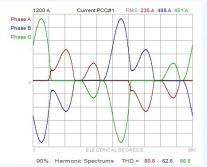

• Example of a Weak System Waveform Trace- 6 Pulse Rectification

\*\*Part | Part | P

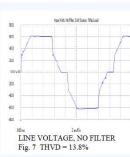

- \* Current Harmonics are load based, – Ithd is the measurement of the non-linear (nonsinusoidal) characteristic of the current draw of the load.

- \* Voltage Harmonics are source based - Vthd (Voltage Distortion) is the result of the injection of the current harmonic into the system impedance; or direct injection via commutative voltage notching.

7

### **Fundamentals of Electrical Harmonics**

- Key Relationships to Understand:

- The lower the Available Short Circuit Current of the Source:

- ~ The lower the regulation of the source, i.e., the weaker the source.

- ~ Any given current harmonic injection will have a lower calculated Ithd but a greater impact on the associated Vthd.

- The greater the Available Short Circuit of the Source:

- ~ The tighter the regulation of the source, i.e., the stiffer the source.

- ~ Any given current harmonic injection will have a higher calculated Ithd but a lower impact on the associated Vthd.

- Key Relationships to Understand:

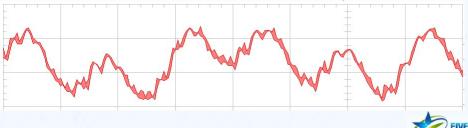

- Any Linear Load Structure fed by a Distorted Source Voltage will run less efficiently and draw current in a non-linear fashion, i.e., will now behave electrically as a nonlinear load.

Above is a wave trace from a 100kW linear load being feed from an IEEE 519-2022 compliant 8% Vthd system.

9

### **Fundamentals of Electrical Harmonics**

- Key Relationships to Understand:

- A distorted voltage (Vthd) supplying a DC Power Supply can create additional DC bus ripple/distortion above the nominal amount, which has a significant impact on all control equipment being supplied by that DC source. The image below shows the effects of low and higher frequency voltage distortion on an AC – DC power supply. This can then create issues for the LV DC components and sensors and transducers effected.

- Key Relationships to understand:

- High speed switching devices, such as IGBT based rectification or inverter applications will create Supraharmonics current characteristics which must be considered and evaluated within a credible harmonic review, modeling program, or testing protocol – typically between 2 kHz and 150 kHz.

11

### **Fundamentals of Electrical Harmonics**

- Key Relationships to understand:

- The greater the source voltage imbalance being provided to a non-linear load, the greater the impact to Current Harmonic (Ithd) and associated Voltage Distortion (Vthd) experienced.

1000 kVA Source - 480V with a 2% Voltage imbalance & 0% Vthd - background distortion

- Key Relationships to understand:

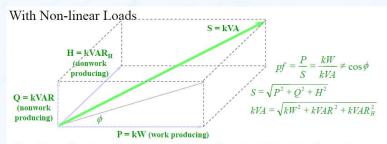

- Current Harmonics have a significant impact on the True/Total Power Factor of the Source, considered as non-work producing Harmonic kVAR (Reactive Power).

True Power Factor = (Displacement Power Factor) x (Distortion Power Factor)

13

### Fundamentals of Electrical Harmonics

Key Relationships to understand:

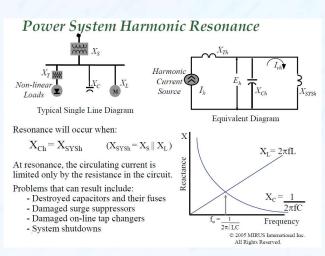

Power systems have a frequency band at which the inductive and capacitive elements are equal. Current harmonic frequencies that are drawn by non-linear loads within this band can result in resonance with the power system.

The result of this Harmonic Resonance can be exhibited in the form of

- ~Voltage Reflective Wave (Ringing),

- ~ Intermittent Voltage Transients

- ~ Elevated levels of Source Background Voltage Distortion (Vthd–bg)

- Key Concepts and Specification Sections:

- The IEEE Std 519-2022 Title. 'Recommended Practice and Requirements' -> 'Standard'

- The goal of the standard is to detail a guideline for ensuring a proper level of Power Quality within the overall distribution system by highlighting

- ~ Recommended Voltage Distortion (Table 1 Voltage Distortion Limits Section 5.1, Pg 17)

- ~ Current Harmonics (Itdd Total Demand Distortion) required levels based on the Available Short Circuit Ratio of the Circuit (Table 2 Current distortion limits for systems rated 120 V through 69 kV, Section 5.3, Page 19 or Table 3 Current distortion limits for systems rated above 69 kV through 161 kV, Section 5.4, Page 20)

- Practically, there will be circuit topologies where you cannot meet IEEE guideline for Voltage Distortion but still comply with requirements of IEEE for Current Harmonics, and visa versa.

15

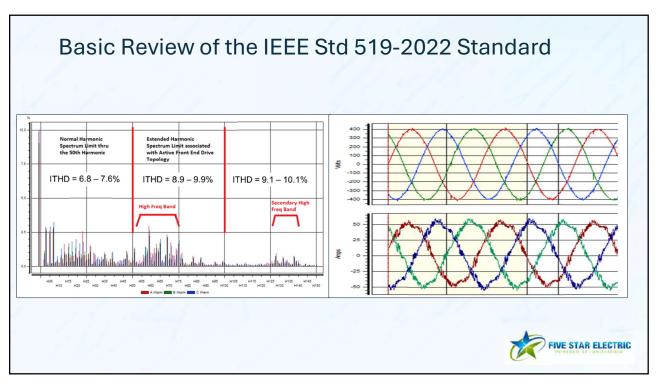

#### Basic Review of the IEEE Std 519-2022 Standard

- Key Concepts and Specification Sections:

- Ithd (Current Total Harmonic Distortion) and Itdd (Current Total Demand Distortion) are not the same thing:

- Ithd is basically a snapshot in time, at a specific load level at the time of test or modeling.

- Itdd is a comparative of the Ithd taken at time of test or modeling as compared to a 12-month peak demand load average or other criteria that would be appropriate to the project and its circumstance.

- New projects may involve a calculated peak demand average or a partial period averaging strategy.

- For further discussion, consult a paper I co-authored and published through Mirus International, "Understanding the Relationship between Current Total Harmonic Distortion (iTHD) and Total Demand Distortion (TDD) in IEEE Std 519-2014", Copyright © 2022-03-30 Mirus International Inc. It is under review for an update to the IEEE Std 519-2022.

- Key Concepts and Specification Sections:

- For DC SCR Harmonic Load Sources, pay close attention to Annex C Limits on commutation notches, since SCR based technologies can and will inject Voltage Distortion directly into the source via the phenomena.

- There is little discussed within the present IEEE Std 519-2022 on Supraharmonics, which is a serious consideration when utilizing IGBT rectification technology. One mention to higher order harmonics is under Paragraph 4. Harmonic measurements – Page 15,

#### 4. Harmonic measurements

For the purposes of assessing harmonic levels for comparison with the limits in this document, any instrument used shall comply with the specifications of IEG 61000.4-7 and IEG 61000.4-30, Class A. IEG 61000.4-30 defines two classes of instruments: Class A and Class S. For Class A instruments, measurements are required to be made at least up to the  $50^{\circ}$  order. However, Class S instruments require measurements only to the  $40^{\circ}$  order. For purposes of IEEE 519 evaluation, measurements shall be made at least up to the  $50^{\circ}$  order. The most relevant protions of the IEG specifications are summarized in 4.1 through 4.4. Research on methods for measurements in the range beyond what is covered by this document are underway.

I would strongly suggest consideration be given to specification of the acceptable Ithd and Itdd levels for higher than 3 kHz (50<sup>th</sup> harmonic) where IGBT switching devices are to be utilized. Refer to "Active Harmonic Mitigation – What the Manufacturers Don't Tell You" Copyright Material IEEE – paper No. PCIC-2018-43, which I co-authored.

17

#### Basic Review of the IEEE Std 519-2022 Standard

- Key Concepts and Specification Sections:

- Under the definitions section of the standard, there is another mention of higher order harmonics within the definition of Total Demand Distortion and Total Harmonic Distortion. This can be used to help qualify your Supraharmonic injection specification. It states:

total demand distortion (TDD): The ratio of the root-mean-square of the harmonic content, considering harmonic components up to the 50th order and specifically excluding interharmonics, expressed as a percent of the maximum demand load current. Harmonic components of order greater than 50 may be included when necessary.

total harmonic distortion (THD): The ratio of the root-mean-square of the harmonic content, considering harmonic components up to the 50th order and specifically excluding interharmonics, expressed as a percent of the fundamental. Harmonic components of order greater than 50 may be included when necessary.

Reference the last line of each, "Harmonic components greater than 50 may be included when necessary."

- Missing Supraharmonic Regulation:

- There is no regulation covering Supraharmonics specifically within the IEEE Std 519-2022 outside of the TDD/THD definitions and Harmonic Measurement section.

This is being referred to as the "Missing Bandwidth" by some and is a significant hole in providing higher frequency harmonic regulation within the electrical standards. Ref: "Active Harmonic Mitigation – What the Manufacturers Don't Tell You" Copyright Material IEEE – paper No. PCIC-2018-43, which I co-authored.

19

- Table 1: Vthd Limits for Voltage Distortion

- Table 1 of the standard highlights the target allowable Voltage Distortion by Voltage Class. Notice the Vthd target decreases as the voltage class increases. Making conformance at greater than 1 kV levels more difficult.

Table 1-Voltage distortion limits

| Bus voltage V at PCC                       | Individual<br>harmonic (%) h ≤ 50 | Total harmonic<br>distortion THD (%) |  |

|--------------------------------------------|-----------------------------------|--------------------------------------|--|

| $V \le 1.0 \text{ kV}$                     | 5.0                               | 8.0                                  |  |

| $1~\mathrm{kV} \leq V \leq 69~\mathrm{kV}$ | 3.0                               | 5.0                                  |  |

| 69 kV $< V \le 161$ kV                     | 1.5                               | 2.5                                  |  |

| 161 kV < V                                 | 1.0                               | 1.5ª                                 |  |

<sup>a</sup>High-voltage systems are allowed to have up to 2.0% THD where the cause is an HVDC terms whose effects are found to be attenuated at points in the network where future users may be

21

#### Basic Review of the IEEE Std 519-2022 Standard

- Table 2: Itdd Limits for Current Harmonics

- The allowable Current Harmonic is a function of the SC ratio of the load versus the Avail. Short Circuit at the Point of Common Coupling (PCC). Once this PCC has been established then you can evaluate the Itdd – Current Total Demand Distortion levels that should be targeted. But, when we measure the Current Harmonic during testing or upon a start-up, this is not Itdd, but instead it is Ithd – Current Total Harmonic Distortion is which fundamentally a snapshot in time based on the Source Vthd-bg and V-imb., as well as that specific load structure.

Table 2—Current distortion limits for systems rated 120 V through 69 kV Converting iTHD to iTDD and Determining

| Maximum harmonic current distortion in percent of $I_{\rm L}$ |           |            |             |             |         |      |  |  |

|---------------------------------------------------------------|-----------|------------|-------------|-------------|---------|------|--|--|

| Individual harmonic order (odd harmonics) <sup>a, b</sup>     |           |            |             |             |         |      |  |  |

| $I_{\rm SC}/I_{\rm L}$                                        | 3 ≤ h <11 | 11≤ h < 17 | 17 ≤ h < 23 | 23 ≤ h < 35 | 35≤h≤50 | TDD  |  |  |

| < 20°                                                         | 4.0       | 2.0        | 1.5         | 0.6         | 0.3     | 5.0  |  |  |

| 20 < 50                                                       | 7.0       | 3.5        | 2.5         | 1.0         | 0.5     | 8.0  |  |  |

| 50 < 100                                                      | 10.0      | 4.5        | 4.0         | 1.5         | 0.7     | 12.0 |  |  |

| 100 < 1000                                                    | 12.0      | 5.5        | 5.0         | 2.0         | 1.0     | 15.0 |  |  |

| > 1000                                                        | 15.0      | 7.0        | 6.0         | 2.5         | 1.4     | 20.0 |  |  |

Compliance:

For an existing system when a one year electrical

iTDD = iTHD x (fundamental current at time of iTHD measurement/average demand current over the previous 12 month period)

$iTDD = iTHD \times (if/iL)$

# Discussion of Load-targeted, Systemic, Partial and Staged Harmonic Mitigation Strategies

Load Target Harmonic Mitigation: Focus Harmonic Mitigation Strategies at the individual load locations, via some form of harmonic cancellation or blocking strategy.

23

## Discussion of Load-targeted, Systemic, Partial and Staged Harmonic Mitigation Strategies

- Load Target Harmonic Mitigation: Focus Harmonic Mitigation Strategies at the individual load locations, via some form of harmonic cancellation or blocking strategy.

- Multiple Strategies may be successfully deployed with caution to understand the

effectiveness and limitations of each strategy as it relates to true circuit condition.

Examples would include Harmonic Filtration (LCL topologies), Phase Shifting and

Multi-pulse Drive deployment, and Active Harmonic Solutions.

- Systemic Harmonic Mitigation: in lieu of targeting individual loads within a circuit for treatment, a viable strategy is to isolate a system harmonic mitigation at the service entrance of the project,. The system strategy can help overcome the cumulative effect of smaller non-linear.

# Discussion of Load-targeted, Systemic, Partial and Staged Harmonic Mitigation Strategies

- Partial Mitigation is a key element. It is based on the concept that you do not have

to treat all the harmonic sources within the circuit, but instead treat/eliminate

enough harmonic contribution from those loads to meet the objectives of IEEE Std

519-2022

- Staged Harmonic Mitigation is more relevant to retrofit applications where project restrictions on funding and/or outage impact must be considered. It can be used for new build installations where the construction project is a staged schedule.

For a more detailed discussion consult a paper I published through Mirus, "A Practical Guide to Partial and Staged Harmonic Mitigation Strategies" TP-006A, 5-12-2020.

25

### Summary of Harmonic Mitigation Methods and Considerations:

Line Reactors & DC Link Inductors:

AC Line Reactors will mitigate the Ithd of the VFD or non-linear load by about 50% by weakening the source, lowering the Ithd seen by the circuit.

- $\sim$  Adds additional impedance lowering the voltage seen by the load

- ~ Increase the current draw at any given load profile and increase the net kW consumed.

- ~Typically, these inductors are sized at 3%, which will increase the energy consumed by approximately the same value.

DC Link Inductors are inductors placed within the DC bus assembly of the VFD to control the DC bus ripple in addition to the DC bus cap. I

~ Impedance of the link inductor is sized by the manufacturer and will have a much lower impact on the overall efficiency of the drive package operation while still lower the Ithd at any given load level by about 50% just like the line reactor.

FIVE STAR ELECTRIC

## Summary of Harmonic Mitigation Methods and Considerations:

Multipulse Drives:

- 12 Pulse VFD's are not harmonically compliant with IEEE 519 guidelines, typical current harmonic levels

will be between 12% for a weak source to over 20% in the case of a stiff source. The drive industry

moved away from this technology over a decade ago.

- 18 Pulse VFD's are typically <u>not</u> compliant with IEEE 519 guidelines in "Real World" Applications. Current 18P technology revolves around the use of Zig-Zag phase shift auto-transformers. This Auto design is not effective with Background Voltage Distortions (Vthd-bg) of 2% or greater or Systemic Voltage Imbalance (Vimb.) of 2% or greater. <u>Notice I said OR not AND</u>. All circuits have a Background Voltage Distortion (Vthd-bg) typically around 1-1/2% to 3% on Light Industrial Systems and can have as much as 12% 16% on Heavy Industrial applications like O&G installations and Offshore Applications. Not only will these two factors impact the harmonic mitigation levels but can also trigger nuisance tripping and VFD failures. Older 18 pulse technologies utilizing isolation 4 winding magnetics are very effective, but seldom available due to cost

- 24 pulse and higher are not often seen currently due to their expense and complexity.

27

## Summary of Harmonic Mitigation Methods and Considerations:

Phase-shift Drive Circuit Topology:

- On multiple VFD loads, a common practice used to be building a phase shift into the distribution grid whereby a 12 pulse or 18 pulse phase shift could be introduced into the source via Utility/Distribution transformers. These involved isolation transformers where the secondary winding utilized an extended delta (0 30^ Phase shift for 12 pulse) or (-20^ 0 +20^ phase shift for 18 pulse for three drives).

- This approach was successful for larger size industrial installations, but it required that each of the VFD's were loaded equally. A mere 2% difference in the load current between the VFD's within the scheme could and would have a significant impact on the performance. Typically, a 3%- or 5 %- line reactor was also integrated into the circuit, which provided an 8% - 10% through impedance to the topology, significantly increasing the losses associated with this applicational strategy.

- I still use this strategy on large industrial projects, less the line reactor but with a passive filter so the

passive filter performance will be enhanced. This will be discussed in a later presentation.

## Summary of Harmonic Mitigations Methods and Considerations:

Active Harmonic Filters (AHF's):

Active Harmonic Filters can be used effectively, but they are prone to have issues with their performance when used on systems that have high background Vd (>5%) and Systemic Voltage Imbalance (>2%). In addition, the harmonic current injection is typically shifted to Supraharmonic frequency ranges in and around the switching frequency of the filter. Sizing of the AHF can be difficult and factors such as displacement power factor must be considered since this can reduce the capacity of the mitigation strategy. The AHF can be expensive relative to its capacity and performance, including the addition of the feeder breaker and startup programming.

Ref: IEEE/PCIC Paper PCIC-2018-43, Active Harmonic Mitigation - What the Manufacturers Don't Tell You.

29

## Summary of Harmonic Mitigations Methods and Considerations:

Passive Filters (LCL Configuration Filters)

- Passive filter technology being marketed today is in most cases being misrepresented since most companies do no detail the Vthd-bg (Source/Background Voltage Distortion) limits of the Systemic Voltage Imbalance Limits (V-imb) within the sales and marketing literature. In most cases, it is buried in the Instruction and Installation manuals and typically ½ or 1% for both individually. Which means in "Real World" applications the advertised performance cannot be meet. It is advisable to specify a passive filter that can meet 8% Ithd with up to 5% Vthd-bg and 3% system voltage imbalance. They are available from multiple vendors.

- Passive filters utilize a capacitance reactance element. Again, in most cases, the detail of the amount of reactance is not divulged until a detailed study of the instruction book is undertaken. In most cases, it is far less expensive to use a high kVAR to kW reactive power ratio design, since capacitors are less expensive than am effective inductor package. This reliance on capacitance reactance versus inductance makes overexcitation of the VFD/Non-linear load at no-load or low load a real concern. In most cases, the Voltage boost at no-load/low-load can easily be 10% which can and will create over-voltage and nuisance trips for the load device. A Capacitor Contactor device may be recommended but this adds additional complexity and cost as well as ineffective harmonic mitigation at low load levels.

## Summary of Harmonic Mitigations Methods and Considerations:

Passive Filters (LCL Configuration Filters)

- Preferred Specification Detail for Passive Filters:

- ITDD must be <8% with background voltage distortion up to 5% and voltage imbalance up to 3%

- Must be capable of operating in voltage distortion environments up to 8% without derating.

- To ensure compatibility with engine generators, the harmonic mitigation equipment must never introduce a capacitive reactive power (kVAR) which is greater than 15% of its kW rating for sizes ≥ 100HP and 20% for sizes ≤ 75HP

- Maximum voltage boost at no load must be < 3% of nominal line voltage.</li>

31

### Questions?

#### **Technical References:**

(Publication Date Order)

- IEEE/PCIC Paper PCIC-2010-15, Design Consideration When Applying Various ASD Topologies to Meet Harmonic Compliance.

- IEEE/PCIC Paper PCIC-2018-43, Active Harmonic Mitigation What the Manufacturers Don't Tell You.

- A Practical Guide to Partial and Staged Harmonic Mitigation Strategies, MIRUS-TP006-A, Michael A McGraw, 05/12/2020

- The Need for Harmonic Modeling and Mitigation in Generator Applications Mike McGraw USA National Sales Manager, Mirus International Inc. Dated 06/24/2021

- An 'Intuitive Understanding' of Electrical Harmonics: A Conversation, Mike McGraw USA National Sales Manager, Mirus International Inc. Dated 03/08/2021

- Understanding the Relationship between Current Total Harmonic Distortion (iTHD) and Total Demand Distortion (TDD) in IEEE Std 519-2014, Group Paper - Mirus International Dated 03/30/2023

- Tutorial Harmonic Challenges for Distribution Grid Design, 3 Hour IEEE Tutorial, IEEE/PES WNC Chapter, 03/05/2024

33

#### Presenter Publication Bio: Michael A. McGraw

IEEE Engineering Credits:

Guest Lecturer Baton Rouge IAS Technical Seminars 2012, 2013, 2014, 2015, 2016, 2017, 2019, 2021. Technical Presenter ETC 2017, 2018, 2019, 2021 Houston TX. IEEE Presenter: NAPS Conference - Oct 15th, 2023, "Overview - Harmonic Challenges for Distribution Grid Design" IEEE Presenter: 3 Hour Tutorial - Region 3, Mar 7th, 2024, Location: Aegis Power Systems, - Murphy, NC

#### IEEE PCIC Conference Published Papers and Awards

- IEEE/PCIC 2010 San Antonio TX, Coauthor, "Design Considerations When Applying Various ASD Topologies to Meet Harmonic Compliance" (PCIC-2010-15), IEEE/PCIC Third Best Paper 2010 Technical conference Award, San Antonio TX

- IEEE/PCIC 2014 San Francisco CA, Coauthor, "Preventing Centrifuge Failures Due To Voltage Distortion On A Drilling Rig" (PCIC-2014-24)

- IEEE/PCIC 2015 Houston TX, Coauthor, "Rightsizing Generators Through Harmonic Mitigation Realizes Energy, Emissions, and Infrastructure Reductions" (PCIC-2015-

- IEEE/PCIC 2016 Philadelphia PA, Coauthor" Marine Duty Harmonic Mitigation ON DC Propulsion Saves Oil Service Vessel Program" (PCIC-2016-38)

- IEEE/PCIC 2018 Cincinnati OH, Co-Author "Active Harmonic Mitigation What the Manufacturers Don't Tell You" (PCIC-2018-43)

- 2018 European PCIC Technical Presenter and Co-Author on the subject of active front end drives and parallel harmonic filters and the injection of higher order harmonics into distribution grids. "Active Harmonic Mitigation - What the Manufacturers Don't Tell You", Europe Paper No. PCIC EUR18\_15

- IEEE/PCIC 2019 Vancouver BC Canada, Co-Author, "A Practical Application of a Sinewave Filter to Resolve ESP Motor Failures" (PCIC-2019-34) IEEE/PCIC Third Best Paper 2019 Technical Conference Award

- IEEE/PCIC 2022 Denver Co. Paper/Abstract Topic selected for development and presentations at the IEEE/PCIC 2024 Conference, "Understanding the Relationship between Current Total Harmonic Distortion (iTHD) and Total Demand Distortion (TDD) in IEEE Std 519-2014: A Practical Discussion for Compliance Evaluations."

- NAPS Symposium 2023 IEEE PES Presentation, Asheville NC: Overview: Harmonic Challenges for Distribution Grid Design

#### Secondary Paper Publishing:

- $Linked In \ Article \ submittals \ covering \ a \ wide \ range \ of \ subjects \ on \ Harmonics \ and \ Harmonic \ Mitigation.$

- Mirus Company White Papers including Primary author status on:

Mirus Series AUSF Inversine Sinewave Mirus Series AUSF Inversine Sinewave Filter versus dV/dT Filter Discussion Filter: San Antonio Water Authority Case Review

- The Modern Hospital/Health Care Environment & Harmonics

- Optimal Transformer Efficiency Using Weighted Average

- $\label{thm:conversation} \textbf{The Need for Harmonic Modeling and Mitigation in Generator Applications: A Conversation and Guide Conversati$

- An 'Intuitive Understanding' of Electrical Harmonics: A Conversation